Accelerated Design Process

In today’s world of smart terminals, silicon chips are part of almost all of them. And almost all of these terminals need to operate reliably over long periods of time.

The CHIPOLY team has achieved SPICE-level simulation accuracy with extremely fast simulation speed and gold standard simulation accuracy by using the Curatorx family of tools. This can project the lifetime of the chip production line, improve chip yield, reduce chip design redundancy, and give full play to the advantages of high process chips.

Improve Chip Yields

Electromigration is a challenge for advanced process chip design. Using Curator to model and accurately simulate important physical parameters for electromigration during the execution of the digital design flow allows engineers to identify and fix problems early on, thus avoiding higher device currents, narrower metal lines, higher temperatures on the die resulting in interconnect reliability and possible EM degradation.

Curator Key Features

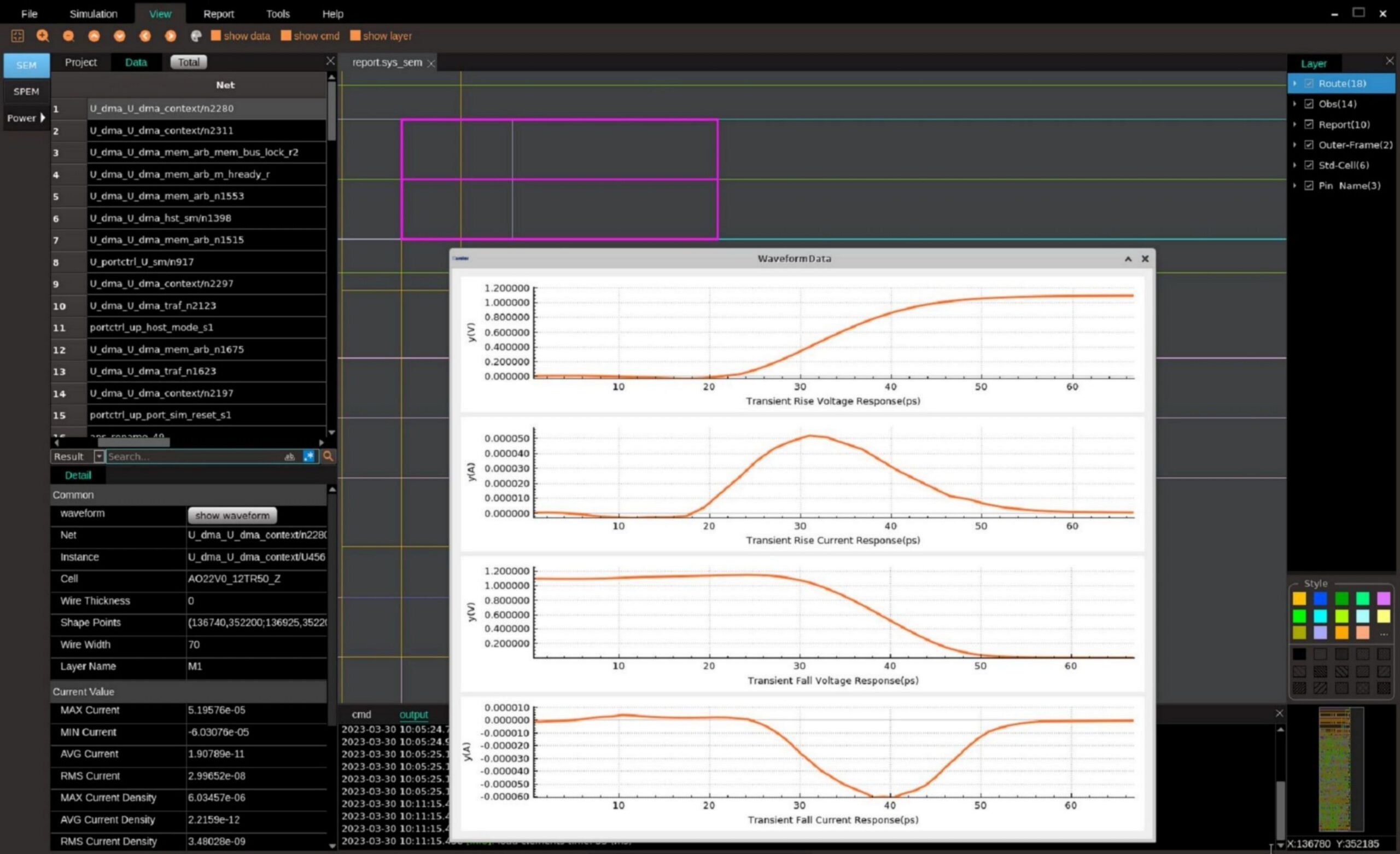

- Full-chip Signal EM analysis and can output signal line transient voltage and current simulation waveforms for more accurate analysis results

- Power calculation support a variety of power calculation methods

- Static power integrity verification, support Static Power EM/IR-drop analysis

- Dynamic power integrity verification, support Dynamic Power EM/voltage drop analysis

- Multi-dimensional, easy-to-read analysis result reports, including text format and graphical format

- Custom CPU cores to run the software

- GUI helps to quickly locate design defects

- EMIR stage fully automatic ECO optimization function